БИС буферных регистров КР580ИР82

БИС КР580ИР82 - микросхема 8-разрядного адресного регистра, предназначенная для связи микропроцессора с системной шиной; обладает повышенной нагрузочной способностью. Микросхема представляет собой восьмиразрядный D-регистр с "защелкой" без инверсии и с тремя состояниями на выходе.

Микросхема состоит из восьми одинаковых функциональных блоков и схемы управления.

В зависимости от состояния стробирующего сигнала STB микросхемы могут работать в двух режимах: в режиме шинного формирователя или в режиме хранения. При высоком уровне сигнала STB и низком сигнале ОЕ микросхема работает в режиме шинного формирователя. При переходе сигнала STB из состояния высокого уровня в низкий происходит "защелкивание" передаваемой информации во внутреннем триггере, и она сохраняется до тех пор, пока на входе STВ присутствует напряжение низкого уровня.

Выходные буферы микросхемы КР580ИР82 управляются сигналом ОЕ "Разрешение выхода". При переходе сигнала ОЕ в состояние высокого уровня все выходы Q переходят в высокоомное состояние независимо от входных сигналов STB и Q. При возвращении сигнала ОЕ в состояние низкого уровня выходы Q переходят в состояние, соответствующее внутренним триггерам.

|

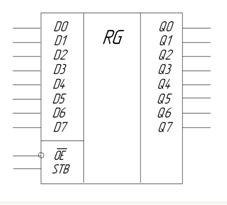

Рисунок 1 - УГО БИС буферного регистра КР580ИР82

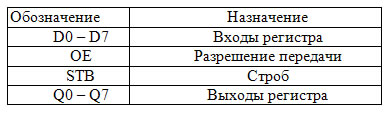

Таблица 1 - Назначение выводов буферного регистра КР580ИР82